#### IEAESP2020-034

**Project Title: A 25 LEVEL ASYMMETRIC MULTILEVEL INVERTER FOR RENEWABLE SOURCES Guide Details** Guide Name: Vijayaraja L Guide Email: vijayarajal.eee@gmail.com Guide Phone No.: 9884298051 **Qualification : M.Tech Department : Electrical and Electronics Engineering** institute name : Sri Sairam Institute of Technology College address : Sri Sairam Institute of Technology, Sai Leo Nagar, West Tambaram, Chennai - 600044 **Students Details** Project Team Leader Name: Yamini Priya D Email: yaminidayanithi15@gmail.com Phone No. : 7397407080 Team Members List : Suga Priya.R, Suvedha.G, Swetha Shirly.S

# TITLE: A 25 LEVEL ASYMMETRIC MULTILEVEL INVERTER FOR RENEWABLE SOURCES

# ABSTRACT

In this generation, multilevel inverter is suitable for high-voltage and high-current applications. This project proposes the design and implementation of a 25 level asymmetric inverter using four sources and ten switches. The proposed system consists of four sources which are asymmetrical in nature. Different structures of MLI were developed by researches and academic in order to reduce the switch count and cost. The proposed design is framed by T-type and Cascaded H-bridge MOSFET based voltage source inverter. In this topology staircase output voltage of twenty-five level is generated with minimum components count. This designed topology can be used in various voltage sources by using renewable energy sources to obtain inverted output.

## LITERATURE SURVEY

| Author details and Title of the paper                                                                         | Work presented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and H. Wu, "Hybrid Multi- Carrier<br>PWM Technique Based on Carrier<br>Reconstruction for Cascaded H-bridge   | The aforementioned technique uses the carrier<br>segment in the half carrier period of the IPD-PWM<br>technique as the basic unit and optimizes the<br>modulation performance by periodically adjusting its<br>arrangement in the vertical direction. When CHB<br>multilevel inverter adopts Hybrid Multi-carrier PWM<br>technique, as with CPS-PWM technique, the output<br>power balance between the cascaded H-bridge cells<br>is achieved naturally; at the same time, the harmonic<br>spectrum of the output voltage is identical with thatof<br>the IPD-PWM technique, that is to say, the harmonic<br>characteristics of the output line voltage of the<br>inverters are effectively improved. |

| Song and S. Li, "Research on Power-<br>Balance Control Strategy of CHB<br>Multilevel Inverter Based on TPWM," | By selecting an appropriate trapezoidal wave<br>triangulation rate $\delta$ , the modulation strategy can<br>greatly increase the amplitude of the CHB inverter<br>output voltage fundamental wave while ensuring the<br>waveform quality of output phase voltage, and realize<br>the power-balance of H-bridge units within a full<br>modulation ratio range by changing the arrangement<br>of triangular carriers in the vertical direction while<br>using the carrier segment in the half carrier period of<br>the IPD-TPWM strategy as the basicunit.                                                                                                                                             |

٦

| S. Naik and A. K. Panda, "A Fuzzy<br>Logic Based Switching Methodology<br>for a Cascaded H-Bridge Multi-Level<br>Inverter," in <i>IEEE Transactions on</i>                                              | The proposed technique simplifies the conventional<br>method by eliminating the traditional logic gate<br>design. The fuzzy logic pulse generator acts as alook-<br>up table as well as a pulse generator. Based on the<br>modulation index as input, controlled membership<br>functions (MFs) and rules of the fuzzy logic controller<br>(FLC) opens various possibilities in producing pulses<br>directly. The proposed technique is evaluated on the<br>cascaded multilevel inverter with symmetric and                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P. R. Bana, K. P. Panda, R. T. Naavagi,                                                                                                                                                                 | asymmetric operations using selective harmonic<br>elimination pulse width modulation (SHE- PWM).<br>To assist with advanced current research in this field                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P. Siano and G. Panda, "Recently<br>Developed Reduced Switch Multilevel<br>Inverter for Renewable Energy<br>Integration and Drives<br>Application:Topologies,Comprehensiv<br>e Analysis and Comparative | and in the selection of suitable inverter for various<br>applications, significant understanding on these<br>topologies is clearly summarized based on the three<br>categories, i.e., symmetrical, asymmetrical, and<br>modified topologies. This review paper also includes<br>a comparison based on important performance<br>parameters, detailed technical challenges, current<br>focus, and future development trends. By a suitable<br>combination of switches, the MLI produces a staircase<br>output with low harmonic distortion.                                                                                                |

| Shah and M. A. Memon, "Optimal<br>Design of a New Cascaded Multilevel<br>Inverter Topology with Reduced                                                                                                 | Multilevel inverters (MLIs) are a great development<br>for industrial and renewable energy applications due<br>to their dominance over conventional two-level<br>inverter with respect to size, rating of switches, filter<br>requirement, and efficiency. The proposed MLI<br>topology is designed with the aim of reducing the<br>number of switches and the number of dc voltage<br>sources with modularity while having a higher<br>number of levels at the output. For the determination<br>of the magnitude of dc voltage sources and a number<br>of levels in the cascade connection, three different<br>algorithms are proposed. |

# HARDWARE/SOFTWARE REQUIRED

- Step down transformer

- Battery

- MOSFET(IRF 840)

- Diode

- Resistors

- Microcontroller(PIC 16F877A)

#### **DESIGN AND METHODOLOGY**

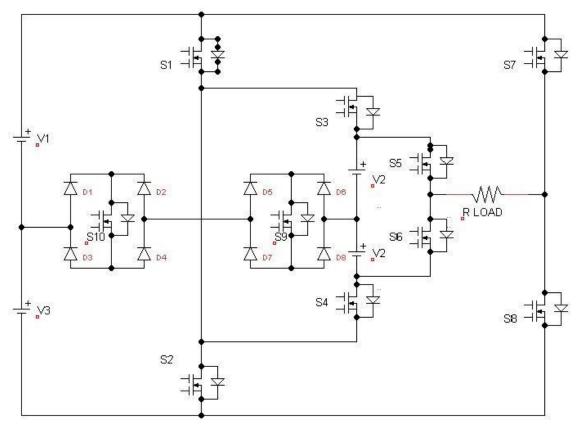

Using the MatLab simulink the proposed inverter is designed. Fig. 1 gives the topology [16] consist of 8 unidirectional switches from S1 – S8 along with two bidirectional switches from S9 – S10. The proposed topology is asymmetric in nature, magnitude of dc- voltage sources are unequal and are given as V1=V3=Vdc and V2=5Vdc. Using this configuration it can generate 25 output voltage level and the switching state is shown in theTable 1 where – denotes on state and \* denotes off state of the switches in the fig 1. Thus 25-L is achieved by below switching sequence. The obtained results from the scope are analyzed.

Figure 1.1. Proposed 25 level Topology [16]

| Vo    | <b>S</b><br>1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | S1<br>0 |

|-------|---------------|----|----|----|----|----|----|----|----|---------|

| 12Vdc | -             | *  | *  | -  | -  | *  | *  | -  | *  | *       |

| TIVdc | *             | *  | *  | -  | -  | *  | *  | -  | *  | -       |

| 10Vdc | -             | *  | *  | -  | -  | *  | -  | *  | *  | *       |

| 9Vdc  | *             | *  | *  | -  | -  | *  | -  | *  | *  | -       |

| 8Vdc  | *             | -  | *  | -  | -  | *  | -  | *  | *  | *       |

| 7Vdc  | -             | *  | *  | *  | -  | *  | *  | -  | -  | *       |

| 6Vdc  | *             | *  | *  | *  | -  | *  | *  | -  | -  | -       |

| 5Vdc  | -             | *  | *  | *  | -  | *  | -  | *  | -  | *       |

| 4Vdc  | *             | *  | *  | *  | -  | *  | -  | *  | -  | -       |

| 3Vdc  | *             | -  | *  | *  | -  | *  | -  | *  | -  | *       |

| 2Vdc  | -             | *  | -  | *  | -  | *  | *  | -  | *  | *       |

| Vdc   | *             | *  | -  | *  | -  | *  | *  | -  | *  | -       |

## Table 2. Switching state for proposed 25 Level topology.

| 0      | - | * | - | * | _ | * | - | * | - | - |

|--------|---|---|---|---|---|---|---|---|---|---|

|        |   |   | - |   | - |   | - |   | - | _ |

| -Vdc   | * | * | * | - | * | - | * | - | * | - |

| -2Vdc  | * | - | * | - | * | - | - | * | * | * |

| -3Vdc  | - | * | * | * | * | - | * | - | - | * |

| -4Vdc  | * | * | * | * | * | - | * | - | - | - |

| -5Vdc  | * | - | * | * | * | - | * | - | - | * |

| -6Vdc  | * | * | * | * | * | - | - | * | - | - |

| -7Vdc  | * | - | * | * | * | - | - | * | - | * |

| -8Vdc  | - | * | - | * | * | - | * | - | * | * |

| -9Vdc  | * | * | - | * | * | - | * | - | * | - |

| -10Vdc | * | - | _ | * | * | _ | * | - | * | * |

| -11Vdc | * | * | - | * | * | - | - | * | * | - |

| -12Vdc | * | - | - | * | * | - | * | - | * | * |

#### Simulation study and Hardware development

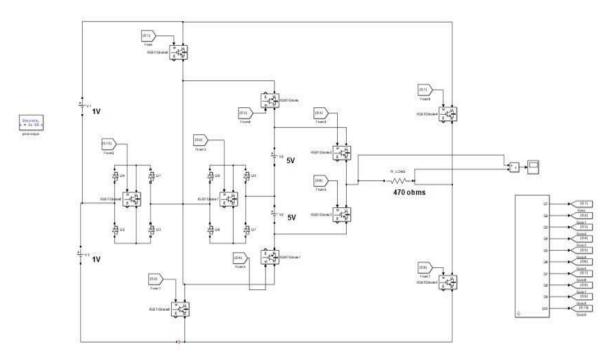

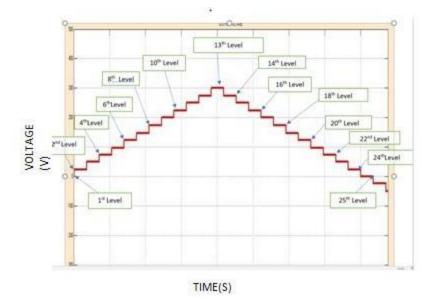

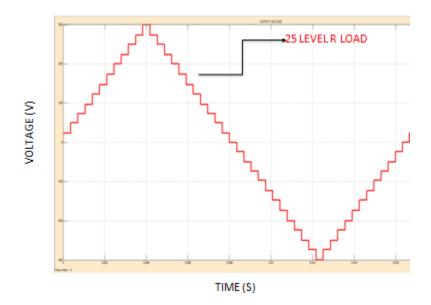

To verify the proposed MLI design, Simulation study has been carried out using MATLAB SIMULINK with R-Load(R=470 ohms). Simulation design output have been shown in Fig 1.2 which as achieved 25 level by connecting four voltage source V1=V3=Vdc and V2=5Vdc and a load resistance of 470 ohms with eight unidirectional switches from S1-S8 and two bidirectional switches from S9-S10 .Thus 25 Level has been achieved by the experimental prototype.

Figure 1.2. Simulation Model of Proposed System

Figure 1.3. Simulation Result For 1 Cycle Of 25 Level Inverter

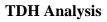

Figure 1.5. THD Analysis of resistive load

The THD analysis of 4S-25 level has been analyzed and the THD value obtained is about 13.46% for a R load of  $470\Omega$ .

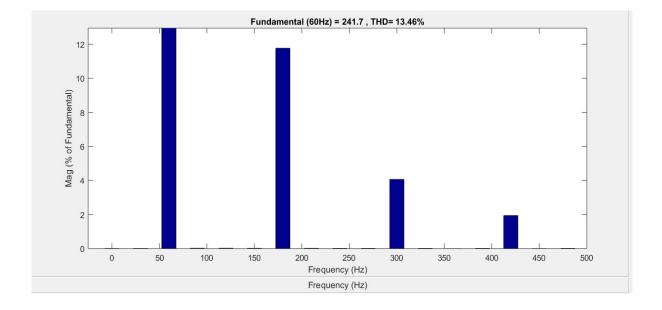

# IMPLEMENTATION

The hardware circuit diagram shown in fig 6 is developed as an experimental prototype and it is depicted in Fig.7. The setup uses four sources and ten switches and it is tested with  $470\Omega$  resistive load. The experimentation yields 25-L at the resistive load and it is captured in CRO shown in fig 8. Hence the staircase output voltage of the 25-Level is generated with minimum components count.

Figure 1.6. Hardware circuit diagram

Figure 1.7. The Inverter Topology Experimented with R Load (R= $470\Omega$ )

Figure 1.8. Output voltage of 25 level inverter with R Load (R=470 $\Omega$ )

## RESULTS

Based on the tests done, the output is measured and found to be matching with the experimental values. The simulation study also taken and every result are found to be coherent.

# CONCLUSION

The presented design yields 25-L at the output. The simulation and experimentation work is carried out to view the operation of the inverter. The comparison between experimental and simulation wave forms further confirms the validity of the proposed multilevel inverter Topology is better. This topology can find suitable place in renewable energy applications, toprovide a small sinusoidal waveform at load.

#### **OTHER REFERENCE**

- [1] L. Vijayaraja, S. G. Kumar and M. Rivera, "A review on multilevel inverter with reduced switch count," 2016 IEEE International Conference on Automatica (ICA-ACCA), Curico, 2016, pp. 1-5, doi: 10.1109/ICA-ACCA.2016.7778467.

- [2] B. Ganesh et al., "Implementation of Twenty seven level and Fifty one level Inverter using constant voltage sources," 2019 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), Valparaiso, Chile, 2019, pp. 1-4.

- [3] G. Raman, A. Imthiyas, M. D. Raja, L. Vijayaraja and S. G. Kumar, "Design of 31level Asymmetric Inverter with Optimal Number of Switches," 2019 IEEE International Conference on Intelligent Techniques in Control, Optimization and Signal Processing (INCOS), Tamilnadu, India, 2019, pp. 1-3, doi: 10.1109/INCOS45849.2019.8951354.

- [4] S. S. Lee, C. S. Lim, Y. Siwakoti and K. Lee, "Dual-T-Type 5-Level Cascaded Multilevel Inverter (DTT-5L-CMI) with Double Voltage Boosting Gain," in IEEE Transactions on Power Electronics.

- [5] D.Niuet al., "A Novel Switched-Capacitor Five-Level T-Type Inverter," 2019 2nd International Conference on Smart Grid and Renewable Energy (SGRE), Doha, Qatar, 2019, pp. 1-6.

- [6] B. Chokkalingam, A. Yusuff, M. Tariq and T. Bhekisiph, "Torque-Ripple Mitigation for BLDC using Integrated Converter Connected Three-Level T Type NPC-MLI," 2019 International Conference on Electrical, Electronics and Computer Engineering (UPCON), ALIGARH, India, 2019, pp. 1-6.

- [7] S. Kumar, J. Kumar and A. Kumari, "A Nine Level Asymmetrical Multilevel Topology for Grid Connected PVGS,"2019 International Conference on Electrical, Electronics and Computer Engineering (UPCON), ALIGARH, India, 2019, pp. 1-6.

- [8] C. B. Barthet al., "Design and Control of a GaN-based, 13-level, Flying Capacitor Multilevel Inverter," in IEEE Journal of Emerging and Selected Topics in Power Electronics.